IBM Research, GlobalFoundries and Samsung partnered to create transistors for a 5-nanometer semiconductor chip, expected to enable chips with 30 billion transistors. Researchers say the technical achievement should enable the $330 billion chip industry to keep up with Moore’s Law, the 1965 statement by Intel chairman emeritus Gordon Moore that the number of transistors per square inch on integrated circuits would double about every two years. Three years ago, IBM vowed to invest $3 billion over five years in chip R&D.

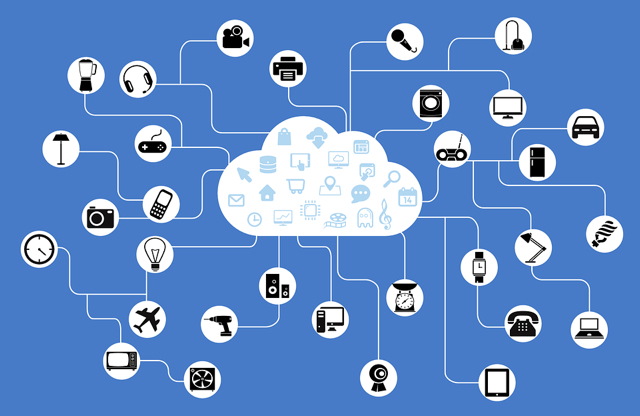

VentureBeat reports that IBM has stated that, “the resulting increase in performance will accelerate cognitive computing, the Internet of Things (IoT) and other data-intensive applications delivered in the cloud.”

The chip will also help manufacturers meet “the future demands of artificial intelligence (AI) systems, virtual reality and mobile devices.” In addition, with the technology’s power savings, smartphones and other mobile devices’ batteries could last two to three times longer than today’s products.

The achievement “comes less than two years since IBM researchers made a 7-nanometer test node chip with 20 billion transistors.” Five nanometers, which is “just a few atoms thick,” can perform 40 percent faster than a 10-nanometer chip or be 75 percent more power efficient, says IBM Research vice president of semiconductor technology research Mukesh Khare.

“This is a major innovation for scaling beyond 7 nanometers,” he said. “It’s an innovation in design and how you pack more and more transistors together. This transistor structure will enable a path to true five nanometers.”

The IBM-headed Research Alliance at SUNY Polytechnic Institute used “stacks of silicon nanosheets for the transistor, instead of the standard FinFET architecture, which is the blueprint for the semiconductor industry up through 7 nanometers.”

Khare reports that IBM Research has “explored [nanosheets] for more than 10 years.” Although the prevailing FinFET technology can produce chips that “scale to 5 nanometers … simply reducing the amount of space between fins does not provide increased current flow for additional performance,” provided by nanosheets.

Other benefits are that nanosheets “can be built using the same manufacturer steps and processes used in 10-nanometer manufacturing,” and that the technology’s flexibility “permits the fine-tuning of performance and power for specific circuits.”

No Comments Yet

You can be the first to comment!

Sorry, comments for this entry are closed at this time.